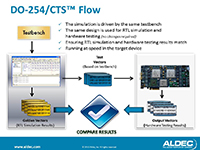

FPGA Test System

DO-254/CTS™ is a fully customized hardware and software platform that augments target board testing to increase verification coverage by test and satisfy the verification objectives of DO-254/ED-80. The target design runs at-speed in the target device mounted on the custom daughter board. The simulation testbench is used as test vectors to enable requirements-based testing with 100% FPGA pin-level controllability and visibility necessary to implement normal range and abnormal range tests. The FPGA testing results are captured at-speed and displayed using a simulator waveform viewer for advanced analysis and documentation.

Top Features

|

- Featured

- Demonstration Video

- DO-254 CTS Overview

- Recorded Webinar

DO-254 - How to Increase Verification Coverage by Test (Aldec and Altera)- DO-254 Requirements Traceability

- Managing Requirements-Based Verification for Safety-Critical FPGAs and SoCs

- Best Practices for DO-254 Requirements Traceability

- Verification of PCIe-based FPGA Designs Requiring DO-254 Compliance

- How to enforce HDL coding standards and gain the overall design review to meet DO-254 objectives

- The impact of AMC-152A guidance on design and verification process of DO-254 projects

- ISO-26262 and DO-254 Achieving Compliance to Both

- Tool Qualification – DO-254, DO-330, and ISO 26262 Approaches

- Managing DO-254 Compliant Documents

- How to plan a DO-254 compliant verification process for FPGA designs

- Shortening the verification time of safety critical projects

- Designing Finite State Machines for Safety Critical Systems

- Common Testbench Development for Simulation and Prototyping

- White Paper

- Aldec DO-254 Solutions Blueprint

- DO-254: Increasing Verification Coverage by Test