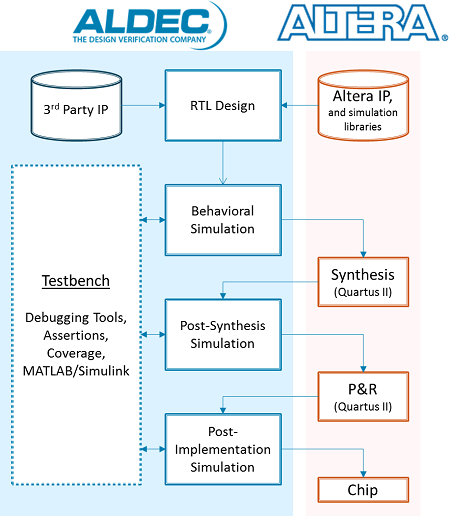

Altera Design Flow

Introduction

Aldec tools provide native interface to Altera’s Quartus II design software that supports all the FPGA and CPLDs devices from Altera. Aldec has partnered with Altera to provide a seamless integration to our mutual customers in terms of device support, libraries support and integration with GUI.

Device Family Support

Aldec tools support all the FPGA and SoC devices from Altera which includes all the devices from Cyclone, Arria and Stratix family. Aldec also supports MAX series devices which is part of CPLD family from Altera.

Libraries Support

Users can use EDA simulation library compiler utility from Altera to compile simulation libraries themselves. EDA simulation library compiler utility from Altera supports both Active-HDL and Riviera-PRO.

Aldec also provides pre-compiled VHDL and Verilog libraries for Altera devices which users can download from Aldec website anytime.

Integration with GUI

Aldec Active-HDL and Riviera-PRO are officially supported EDA simulators by Altera Quartus II software for RTL and Gate level simulations. Simulating Altera designs in Aldec tools involve setting up work environment, compiling simulation libraries and running the simulation.

Simulation of IP Cores

All the IP cores generated by Quartus II software are supported by Aldec tools. Quartus II generates IP simulation script that allows users to run the simulation of IPs directly using scripts.

Simulating IP Cores in Aldec tools

Legacy Design Import

Aldec supports importing HDL based legacy designs from Altera’s MAX+PLUS II software. All the HDL files from the legacy projects can be fully imported to Aldec tools. These HDL files then can be edited to retarget to a modern devices from Altera.

Using Aldec as default simulator:

Simulating processor-based systems:

System integration:

Related Aldec products:

Simulating with Altera libraries:

Corporate Headquarters

2260 Corporate Circle

Henderson, NV 89074 USA

Tel: +1 702 990 4400

Fax: +1 702 990 4414

https://www.aldec.com

©2026 Aldec, Inc.