Functional Verification

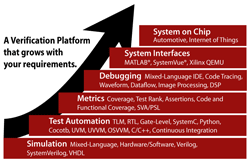

Riviera-PRO™ addresses verification needs of engineers crafting tomorrow’s cutting-edge FPGA and SoC devices. Riviera-PRO enables the ultimate testbench productivity, reusability, and automation by combining the high-performance simulation engine, advanced debugging capabilities at different levels of abstraction, and support for the latest Language and Verification Library Standards.

Top Features and Benefits

High Performance Simulation

- Extensive simulation optimization algorithms to achieve the highest performance in VHDL, Verilog/SystemVerilog, SystemC, and mixed-language simulations

- The industry-leading capacity and simulation performance enable high regression throughput for developing the most complex systems

- Support for the latest Verification Libraries, including Universal Verification Methodology (UVM)

- Support for VHDL verification libraries, including OSVVM and UVVM.

Advanced Debugging

- Integrated multi-language debug environment enables automating time-consuming design analysis tasks and fixing bugs quickly

- UVM Toolbox, UVM graph, Class Viewer, Transaction streams and data to allow visual mapping and debugging of designs based on OVM/UVM class libraries

- Built-in debugging tools provide code tracing, waveform, dataflow, FSM window, coverage, assertion, and memory visualization capabilities

- Comprehensive Assertion-Based Verification (SVA and PSL) for increased design observability and decreased debug time

- Advanced Code and Functional Coverage capabilities and Coverage analysis tools for fast metric-based verification closure

- Efficient verification flow with user-defined test plan linking with coverage database

- Plot viewer and Image viewer tools for visual representation of large arrays of data.

Industry’s Best ROI

- Riviera-PRO enables Aldec customers to deliver innovative products at a lower cost in shorter time

- Features partnerships and integrations necessary to build complete design and verification flows

- Deployment of any Aldec solution is accompanied by comprehensive training and support

- Featured

- Demonstration Video

1.0 Riviera-PRO™ Overview: Advanced Verification Platform- Recorded Webinar

- Engineering best practices for Python-based testbenches with cocotb

- Automating UVM flow using Riviera-PRO’s UVM Generator

- Using SVA for Requirements-Based Verification of Safety-Critical FPGA Designs

- Assertions-Based Verification for VHDL Designs

- Optimizing Simulations for Efficient Coverage Collection

- Addressing the Challenges of SoC Verification in practice using Co-Simulation

- OSVVM: ASIC level VHDL Verification, Simple enough for FPGAs

- Effective Testbench Creation Using Cocotb and Python

- Verifying Resets and Reset Domain Crossings

- Taming Testbench Messaging and Error Reporting with OSVVM's Logs and Alerts

- Universal VHDL Verification Methodology (UVVM) – The standardized open source VHDL testbench architecture

- VHDL testbenches using models, scoreboards and transactions

- Creating an AXI4 Lite, Transaction Based VHDL Testbench with OSVVM

- UVVM steps up a gear: A review of some of the new features in this standardized VHDL verification methodology

- Designing Finite State Machines for Safety Critical Systems

- Common Testbench Development for Simulation and Prototyping

- Creating Better Self-Checking FPGA Verification Tests with Open Source VHDL Verification Methodology (OSVVM)

- UVM Simulation-based environment for Ibex RISC-V CPU core with Google RISC-V DV

- UVM-based Verification of Custom Instructions with RISC-V Cores

- High-Performance PCIe 5.0 IP + VIP UVM Verification Environment

- Debugging Multi-Core Designs using Vitis + Aldec Riviera-PRO Co-Simulation for Zynq US+ MPSoC

- Accelerating Verification Component development with OSVVM Model Independent Transactions

- Functional Verification of Clock Domain Crossing Issues

- Fast Track to Riviera-PRO, Part 1: Design Entry and Simulation

- Fast Track to Riviera-PRO, Part 2: Advanced Debugging, Code Coverage and Scripting

- The impact of AMC-152A guidance on design and verification process of DO-254 projects

- VHDL-2019: Just the New Stuff Part 1: Interfaces, Conditional Analysis, File IO, and The New Environment

- VHDL-2019: Just the New StuffPart 2: Protected Types and Verification Data Structures

- VHDL-2019: Just the New Stuff Part 3: RTL Enhancements

- VHDL-2019: Just the New Stuff Part 4: Testbench Enhancements

- OSVVM: The New Stuff

- UVM for FPGAs (Part 1): Get, Set, Go – Be Productive with UVM

- UVM for FPGAs (Part 2): Solving FPGA Verification Challenges with UVM

- UVM for FPGAs (Part 3): Verifying Zynq MPSoC Designs? Learn how UVM Register Access Layer (RAL) can help

- UVM for FPGAs (Part 4): IEEE 1800.2 UVM Updates

- The most error prone FPGA corner cases

- Using OVL for Assertion-Based Verification of Verilog and VHDL Designs

- Constraint Random Verification with Python and Cocotb

- Increase your productivity with Continuous Integration flows

- Application Note

- Controlling Riviera-PRO from MATLAB®

- Tutorial

- Running simulation in the GUI mode

- White Paper

- Using Plots for HDL Debugging as a Powerful Alternative to Traditional Waveforms

- HDL Simulation Acceleration Solution for Microchip FPGA Designs