Aldec Design and Verification Blog

Trending Articles

FPGA Design Verification (Planning) in a Nutshell Before wading into this topic, I’d like to state why I felt compelled to write about FPGA design verification. I recently presented a very well attended three-part webinar series, during which many attendees asked for book recommendations....

Introduction This blog post continues on from “Development of real-time SDR systems with Aldec HES” which was written by Mariusz Grabowski and recounted how the early development phases of a Software Defined Radio (SDR) were achieved using our HES platform....

As telecommunication technologies evolve there is an on-going drive for the development of high-performance systems for radio communications. Part of that evolution involves implementing components in software functions that had traditionally been implemented in hardware....

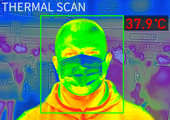

While immunization vaccines are rolling out at an impressive pace, and as society slowly reopens, our best defense against the Coronavirus continues to be early detection and rapid response (such as self-isolation)....

In the early days of digital design, all circuits were designed manually. You would draw K-map, optimize the logic and draw the schematics. If you remember, we all did many logic optimization exercises back in college....

As the open-source RISC-V instruction set architecture (ISA) continues to gain momentum, the growing number of RISC-V design solutions, and their flexibility, creates a problem when choosing the most reliable and robust solution from a number of contenders....

Everyday there are new devices appearing in homes, offices, hospitals, factories and thousands of other places that are part of the Internet-of-Things (IoT). Clearly, they need to be connected to the internet and there is a need for a huge amount of raw data to be collected...

The verification process is long and time consuming, especially when you are not sure what you are looking for. There are a lots of directions you can go looking for bugs but without a guide, without a plan you will most likely be going in circles....

Will the world be a better place in which to live by having autonomous cars driving around us? Or would it be unsafe and scary? Maybe someone was asking such a question even when the first steam-powered automobile capable...

In this blog, I will discuss randomized layered testbenches used in SystemVerilog. We need to understand why we need it,...

.png)

.jpg)

.png)

.png)